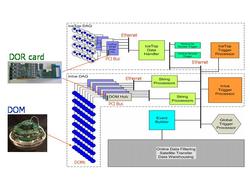

DAQ-Blockdiagramm

IceCube

IceCube–Die DOm Readout (DOR) Karte

Elektronikgruppe Zeuthen

IceCube–Die DOm Readout (DOR) Karte

IceCube-Experiment – Die DOm Readout (DOR) Karte

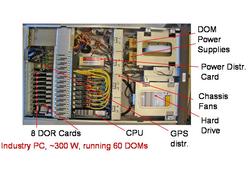

Die DOR-Karte ist ein PCI Businterface. Sie ermöglicht die Datenauslese und Steuerung von 1 bis 8 DOMs (Digital Optical Modulen), ist daher ein wichtiger Bestandteil des ICECUBE Datenerfassungssystems.

|

Die wichtigsten Funktionen sind:

|

|

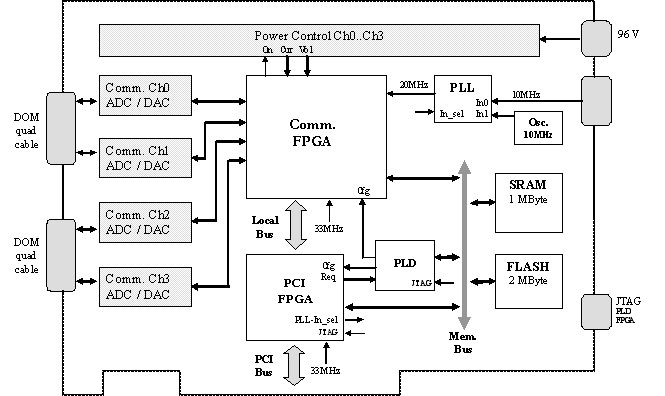

DOR-Blockdiagramm

DOM-Stromversorgung

Die 96V Stromversorgung für jede der 4 Doppelleitungen zur Versorgung von 1 oder 2 (parallel geschalteten) DOMs erfolgt per Software.

- beim Ein- bzw. Ausschalten folgt der Spannungsverlauf einer Rampenfunktion um Stromspitzen sowie Übersprechen (Nachbarleitung) zu minimieren

- Strom und Spannungswerte können ausgelesen werden

- die Firmware unterbricht automatisch die Stromversorgung, wenn Strom- und / oder Spannungswerte außerhalb der Grenzwerte liegen oder der Kabelstecker gezogen wurde

Kommunikation mit den DOMs

Die DOR-Karte steuert als Master die Kommunikation. Der Datenübertragungsmodus ist halb duplex, das Protokoll UART-ähnlich: 1 Start, 8 Daten, and 1 Stopp Bit. Die Kodierung ist gleichspannungsfreies ASK (Amplitude-Shift Keying). Die logische Eins wird durch einen symmetrischen bipolaren Puls repräsentiert, die Null durch das Fehlen eines Signals.

Das Firmware-Kommunikationsprotokoll umfasst u. a. folgende Befehle:

- Data Read Request: Aufforderung an den DOM, Daten zu schicken

- Buffer Status: dient der DOM / DOR Datenpuffer Synchronisation

- Communication Reset: zur Initialisierung

- System Reset: DOM Warmstart

- DOM Reboot: bewirkt ein Reboot des DOMs, z.B. um dort neue geladene Firmware zu aktivieren.

- TCAL Request: per Software einmal pro Sekunde, löst einen etwa 1.3 ms langen Zeitkalibrationszyklus aus, und generiert Zeitkalibrationsdaten. Virtuell haben damit alle DOMs synchron laufende Uhren mit einer Genauigkeit von etwa 1.5 ns

- Idle: Idle-Pakete zur Überprüfung der Kommunikation

- Checksummen-Fehler-Behandlung: alle Pakete haben eine 32 Bit-Checksumme. Die Firmware unterdrückt den Empfang von fehlerbehafteten Daten.

- Hardware Timeout: Wenn ein DOM länger als 4 Sekunden “schweigt”, wird dieser von der Kommunikation ausgeschlossen und der zweite (parallel angeschlossene) DOM bekommt die volle Bandbreite zugewiesen.

Zeitkalibration

Die DOR-Karte bekommt über eine Fanout-Karte (DOM hub Service Board ) 3 Signale von einem GPS-System: 10MHz, 1PPS (pulse per second) und einen seriellen ASCII- Zeitstring.

Die 10 MHz werden auf der DOR-Karte verdoppelt. Die resultierenden 20MHz takten einen 56 Bit Zähler in der DOR-FPGA. Mit Hilfe des PPS-Signals wird jede Sekunde ein Snapshot dieses Zählers genommen. Dieser wird zusammen mit dem dazugehörigen ASCII Zeitstring abgespeichert, um den Zusammenhang zur UTC-Zeit herzustellen. Die Software kann jeder Zeit ein Zeitkalibrationszyklus auslösen. An dessen Ende steht ein per Firmware generiertes Datenpaket zur Verfügung, welches ermöglicht, im DOM erfasste Events mit einer Messgenauigkeit von etwa 1.5ns zu registrieren.

PCI Bus Steuerung

Eine separate Altera-FPGA dient als PCI-Businterface vom Typ Master / Target, lauffähig sowohl auf 5V - als auch auf 3.3V - Plattformen. Die Firmware basiert auf der Verwendung eines kommerziellen PCI-Cores, kompatibel zur PCI Local Bus Specification Revision 2.2 .

Die wichtigsten Funktionen dieser FPGA sind:

- Datentransfer im I/O und DMA Modus

- FLASH Memory lesen und schreiben (FPGA-Images)

- FPGA konfigurieren mit Hilfe einer CPLD

- Steuerung des lokalen Busses (Verbindung zur Kommunikations-FPGA)

- Auswahl der Takt-Quelle für die Kommunikation (GPS oder lokaler onboard-Oszillator)

In System Firmware Update

Die Images (Konfigurations-Daten) für die PCI-Bussteuerungs-FPGA und die Komunikations-FPGA befinden sich in einem 2MB großen Flash Memory. Dieses Memory ist in 4 Seiten unterteilt. Während die Seite 3 für die PCI-Steuerung reserviert ist, sind die Seiten 0...2 der Kommunikations-Firmware vorbehalten.

Nach dem PC-Reset oder initialisiert per Software, startet eine Statemachine in der CPLD, liest das Flash-Memory und konfiguriert mit diesen Daten eine oder beide FPGAs.

Die 2 FPGAs und die CPLD sind mit einer seriellen JTAG chain verbunden. Alternativ, typischer Weise in der Firmware-Design-Phase, können die FPGAs auch auf diese Weise konfiguriert werden.

Die “obere Ecke” des Flash Memories enthält die Seriennummer jeder DOR-Karte sowie individuelle Daten, wie z.B. ADC-Rauschen, ermittelt nach der Herstellung, während der Inbetriebnahme.